Na semana passada, a TSMC divulgou seus relatórios de ganhos do quarto trimestre e do ano inteiro de 2022 para a empresa. Além de confirmar que a TSMC estava encerrando um ano muito movimentado e lucrativo para a maior fabricante de chips do mundo – registrando quase US$ 34 bilhões em receita líquida para o ano – o relatório de final de ano da empresa também nos deu uma nova atualização sobre o estado dos vários projetos fabulosos da TSMC.

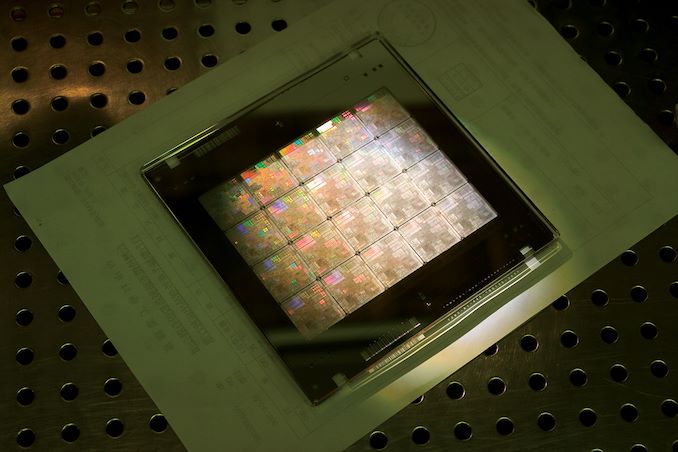

A grande novidade da TSMC para o quarto trimestre de 22 é que a TSMC iniciou a fabricação de alto volume de chips em sua tecnologia de fabricação N3 (classe de 3 nm). A rampa desse nó será bastante lenta inicialmente devido aos altos custos de projeto e às complexidades da primeira implementação N3B do nó, portanto, a maior fundição do mundo não espera que seja uma contribuição significativa para sua receita em 2023. No entanto, o a empresa investirá dezenas de bilhões de dólares na expansão de sua capacidade de fabricação compatível com N3, já que, eventualmente, espera-se que N3 se torne uma família popular e duradoura de nós de produção para TSMC.

Rampa lenta inicialmente

“Nosso N3 entrou com sucesso na produção de volume no final do quarto trimestre do ano passado, conforme planejado, com bom rendimento”, disse C. C. Wei, executivo-chefe da TSMC.”Esperamos um aumento suave em 2023 impulsionado por HPC e aplicativos de smartphone. Como a demanda de nossos clientes por N3 excede nossa capacidade de fornecimento, esperamos que o N3 seja totalmente utilizado em 2023.”

Lembrando que os gastos de capital da TSMC em 2021 e 2022 foram focados principalmente na expansão de suas capacidades de fabricação N5 (classe 5 nm), é não surpreende que a capacidade de N3 da empresa seja modesta. Enquanto isso, a TSMC não espera que o N3 responda por qualquer parcela considerável de sua receita antes do terceiro trimestre.

Na verdade, a fundição nº 1 espera nós N3 (que incluem tanto o N3 básico quanto o N3E relaxado definido como entrar no HVM no segundo semestre de 2023) para representar talvez 4%-6% da receita de wafer da empresa em 2023. E, no entanto, isso excederia a contribuição do N5 em seus dois primeiros trimestres de HVM em 2020 (que foi de cerca de US $ 3,5 bilhões ).

“Esperamos que a [contribuição considerável da receita da N3] comece no terceiro trimestre de 2023 e a N3 contribua com uma porcentagem de meio dígito de nossa receita total de wafer em 2023″, disse Wei.”Esperamos que a receita do N3 em 2023 seja maior do que a receita do N5 em seu primeiro ano em 2020.”

Muitos analistas acreditam que a linha de base N3 (também conhecida como N3B) será usada pela Apple exclusivamente ou quase exclusivamente, que é o maior cliente da TSMC que está disposto a adotar nós de ponta antes de todas as outras empresas, apesar dos altos custos iniciais. Se essa suposição estiver correta e a Apple for de fato o principal cliente a usar a linha de base N3, é digno de nota que a TSMC menciona smartphone e HPC (um termo vago que a TSMC usa para descrever praticamente todos os ASICs, CPUs, GPUs, SoCs e FPGAs não voltado para aplicativos automotivos, comunicações e smartphones) em conjunto com o N3 em 2023.

N3E chegando no segundo semestre

Uma das razões pelas quais muitas empresas estão esperando pelo N3E descontraído da TSMC tecnologia (que está entrando no HVM no segundo semestre de 2023, de acordo com a TSMC) é o maior desempenho e melhorias de energia, bem como uma escala lógica ainda mais agressiva. Outra é que o processo oferecerá custos mais baixos, embora ao custo de um falta de dimensionamento de SRAM em comparação com N5, de acordo com analistas da China Renaissance.

“N3E, com seis camadas EUV a menos do que a linha de base N3, promete complexidade de processo mais simples, custo intrínseco e tempo de ciclo de fabricação, embora com menor ganho de densidade”, escreveu Szeho Ng, analista da China Renaissance, em nota aos clientes esta semana.

Ho diz que o N3 original da TSMC apresenta até 25 camadas EUV e pode aplicar vários padrões para algumas delas para densidade adicional. Por contrato, o N3E suporta até 19 camadas EUV e usa apenas EUV de padrão único, o que reduz a complexidade, mas também significa menor densidade.

“O interesse dos clientes no N3E otimizado (após a linha de base do N3B ramp-up, que é amplamente limitado à Apple) é alto, abrangendo aplicativos de computação intensiva em HPC (AMD, Intel), móvel (Qualcomm, Mediatek) e ASICs (Broadcom, Marvell)”, escreveu Ho.

Parece que o N3E será de fato o principal cavalo de trabalho da classe 3nm da TSMC antes que N3P, N3S e N3X cheguem mais tarde.

Dezenas de bilhões no N3

Enquanto os nós da classe 3nm da TSMC vão render à empresa um pouco mais de US $ 4 bilhões em 2023, a empresa gastará dezenas de bilhões de dólares expandindo sua capacidade fab para produzir chips em vários nós N3. Este ano, os gastos de capital da empresa devem ficar entre US$ 32 bilhões e US$ 36 bilhões. 70% dessa quantia será usada em tecnologias de processo avançadas (N7 e abaixo), que incluem capacidade compatível com N3 em Taiwan, bem como equipamentos para a Fab 21 no Arizona (nós N4, N5). Enquanto isso, 20% serão usados para fábricas que produzem chips em tecnologias especializadas (o que significa essencialmente uma variedade de processos de classe de 28nm) e 10% serão gastos em itens como embalagens avançadas e produção de máscaras.

Gastos em menos US$ 22 bilhões em capacidade N3 e N5 indica que a TSMC está confiante na demanda por esses nós. E há uma boa razão para isso: a família N3 de tecnologias de processo está definida para ser a última família de nós de produção baseada em FinFET da TSMC para chips complexos de alto desempenho. O processo de fabricação N2 (classe de 2nm) da empresa contará com transistores de efeito de campo (GAAFETs) baseados em nanofolhas. Na verdade, o analista Szeho Ng, da China Renaissance, acredita que uma parcela significativa do CapEx deste ano definido para tecnologias avançadas será gasta em capacidade N3, preparando o terreno para a implantação de N3E, N3P, N3X e N3S. Como as fábricas compatíveis com N3 também podem produzir chips em processos N5, a TSMC poderá usar essa capacidade onde também haverá demanda significativa por chips baseados em N5.

“A TSMC orientou o CapEx de 2023 em $ 32-36 bilhões (2022: US$ 36,3 bilhões), com sua expansão focada em N3 na Fab 18 (Tainan)”, escreveu o analista em nota aos clientes.

Como a tecnologia de processo N2 da TSMC só começará a crescer em 2026, o N3 será de fato um nó duradouro para a empresa. Além disso, como será o último nó baseado em FinFET para chips avançados, será usado por muitos anos, pois nem todos os aplicativos precisarão de GAAFETs.