La semana pasada, TSMC emitió sus informes de ganancias del cuarto trimestre y de todo el año 2022 para la empresa. Además de confirmar que TSMC estaba cerrando un año muy ocupado y muy rentable para la principal fábrica de chips del mundo, registrando casi $ 34 mil millones en ingresos netos para el año, el informe de fin de año de la compañía también nos ha brindado una nueva actualización sobre el estado de los diversos proyectos fab de TSMC.

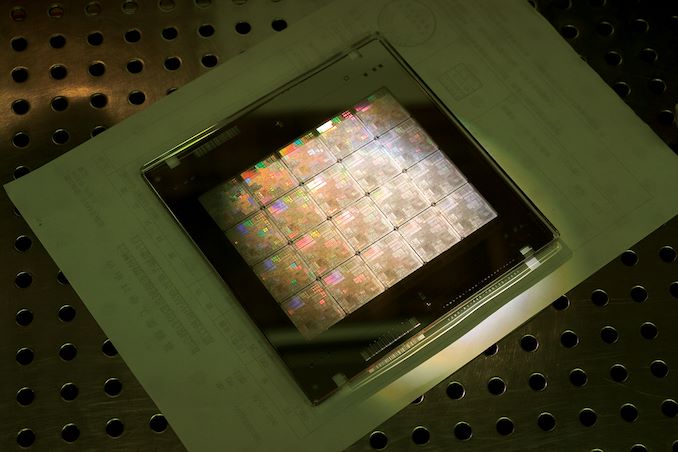

La gran noticia que salió de TSMC para el cuarto trimestre de 2022 es que TSMC ha iniciado la fabricación de alto volumen de chips en su tecnología de fabricación N3 (clase 3nm). La rampa de este nodo será bastante lenta inicialmente debido a los altos costos de diseño y las complejidades de la primera implementación N3B del nodo, por lo que la fundición más grande del mundo no espera que contribuya significativamente a sus ingresos en 2023. Sin embargo, el La empresa invertirá decenas de miles de millones de dólares en la expansión de su capacidad de fabricación compatible con N3, ya que finalmente se espera que N3 se convierta en una popular familia duradera de nodos de producción para TSMC.

Inicialmente rampa lenta

“Nuestro N3 ha entrado con éxito en la producción en volumen a fines del cuarto trimestre del año pasado como estaba previsto, con un buen rendimiento”, dijo C. C. Wei, director ejecutivo de TSMC.”Esperamos una rampa suave en 2023 impulsada tanto por HPC como por aplicaciones de teléfonos inteligentes. Dado que la demanda de N3 de nuestros clientes supera nuestra capacidad de suministro, esperamos que N3 se utilice por completo en 2023″.

Teniendo en cuenta que los gastos de capital de TSMC en 2021 y 2022 se centraron principalmente en expandir sus capacidades de fabricación N5 (clase 5nm), es no sorprende que la capacidad de N3 de la empresa sea modesta. Mientras tanto, TSMC no espera que N3 represente una parte considerable de sus ingresos antes del tercer trimestre.

De hecho, la fundición n.° 1 espera nodos N3 (que incluyen tanto el N3 básico como el N3E relajado que está configurado para ingrese a HVM en la segunda mitad de 2023) para representar quizás el 4%-6% de los ingresos por obleas de la compañía en 2023. Y, sin embargo, esto superaría la contribución de N5 en sus primeros dos trimestres de HVM en 2020 (que fue de aproximadamente $ 3.5 mil millones ).

“Esperamos que [la considerable contribución de ingresos de N3] comience en el tercer trimestre de 2023 y N3 contribuirá con un porcentaje medio de un dígito de nuestros ingresos totales de obleas en 2023″, dijo Wei.”Esperamos que los ingresos de N3 en 2023 sean más altos que los ingresos de N5 en su primer año en 2020”.

Muchos analistas creen que Apple utilizará la línea base N3 (también conocida como N3B) de forma exclusiva o casi exclusivamente, que es el cliente más grande de TSMC que está dispuesto a adoptar nodos de vanguardia antes que todas las demás empresas, a pesar de los altos costos iniciales. Si esta suposición es correcta y Apple es de hecho el principal cliente que usa N3 de referencia, entonces es digno de mención que TSMC menciona tanto el teléfono inteligente como el HPC (un término vago que TSMC usa para describir prácticamente todos los ASIC, CPU, GPU, SoC y FPGA no destinadas a aplicaciones automotrices, de comunicaciones y de teléfonos inteligentes) junto con N3 en 2023.

N3E llegará en la segunda mitad

Una de las razones por las que muchas empresas están esperando el relajado N3E de TSMC (que ingresará a HVM en la segunda mitad de 2023, según TSMC) son las mejoras de mayor rendimiento y potencia, así como una escala lógica aún más agresiva. Otra es que el proceso ofrecerá costos más bajos, aunque a costa de un falta de escalado de SRAM en comparación con N5, según analistas de China Renaissance.

“N3E, con seis capas EUV menos que el N3 de referencia, promete una complejidad de proceso más simple, un costo intrínseco y un tiempo de ciclo de fabricación, aunque con menos ganancia de densidad”, escribió Szeho Ng, analista de China Renaissance, en una nota a los clientes esta semana..

Ho dice que el N3 original de TSMC presenta hasta 25 capas EUV y puede aplicar patrones múltiples para algunas de ellas para una densidad adicional. Por contrato, N3E admite hasta 19 capas EUV y solo usa EUV de patrón único, lo que reduce la complejidad, pero también significa una menor densidad.

“El interés de los clientes en el N3E optimizado (publicar la línea de base N3B rampa-up, que se limita en gran medida a Apple) es alto, y abarca aplicaciones de computación intensiva en HPC (AMD, Intel), dispositivos móviles (Qualcomm, Mediatek) y ASIC (Broadcom, Marvell)”, escribió Ho.

Parece que N3E será el caballo de batalla principal de la clase de 3nm de TSMC antes de que lleguen N3P, N3S y N3X más adelante.

Decenas de miles de millones en N3

Mientras que los nodos de clase de 3nm de TSMC van a generarle a la compañía un poco más de $4 mil millones en 2023, la compañía gastará decenas de miles de millones de dólares en expandir su capacidad fabril para producir chips en varios nodos N3. Este año, los gastos de capital de la compañía se estiman entre $ 32 mil millones y $ 36 mil millones. El 70% de esa suma se utilizará en tecnologías de proceso avanzadas (N7 e inferiores), que incluyen capacidad con capacidad N3 en Taiwán, así como equipos para Fab 21 en Arizona (nodos N4, N5). Mientras tanto, el 20 % se utilizará para fábricas que producen chips en tecnologías especiales (lo que esencialmente significa una variedad de procesos de clase de 28 nm), y el 10 % se gastará en cosas como empaques avanzados y producción de máscaras.

Gasto en menos $ 22 mil millones en capacidad N3 y N5 indica que TSMC confía en la demanda de estos nodos. Y hay una buena razón para ello: la familia de tecnologías de proceso N3 se convertirá en la última familia de nodos de producción basados en FinFET de TSMC para chips complejos de alto rendimiento. El proceso de fabricación N2 (clase 2nm) de la empresa se basará en transistores de efecto de campo de compuerta completa basados en nanohojas (GAAFET). De hecho, el analista Szeho Ng de China Renaissance cree que una parte significativa del CapEx de este año establecido para tecnologías avanzadas se gastará en capacidad N3, sentando las bases para el despliegue de N3E, N3P, N3X y N3S. Dado que las fábricas con capacidad N3 también pueden producir chips en procesos N5, TSMC podrá usar esta capacidad donde también habrá una demanda significativa de chips basados en N5.

“TSMC guió 2023 CapEx a $ 32-36.000mn (2022: US$36.300mn), con su expansión enfocada en N3 en Fab 18 (Tainan)”, escribió el analista en una nota a los clientes.

Dado que la tecnología de proceso N2 de TSMC solo aumentará a partir de 2026, N3 será un nodo de larga duración para la empresa. Además, dado que será el último nodo basado en FinFET para chips avanzados, se utilizará durante muchos años, ya que no todas las aplicaciones necesitarán GAAFET.