La semaine dernière, TSMC a publié ses rapports sur les résultats du quatrième trimestre et de l’année 2022 pour l’entreprise. En plus de confirmer que TSMC clôturait une année très chargée et très rentable pour le premier fabricant de puces au monde – réalisant près de 34 milliards de dollars de bénéfice net pour l’année – le rapport de fin d’année de la société nous a également donné une nouvelle mise à jour sur l’état des divers projets de fabrication de TSMC.

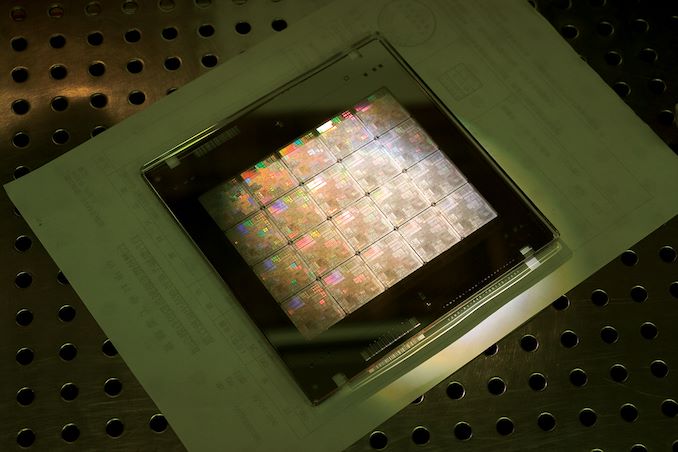

La grande nouvelle qui sort de TSMC pour le quatrième trimestre 22 est que TSMC a lancé la fabrication à haut volume de puces sur sa technologie de fabrication N3 (classe 3 nm). La montée en puissance de ce nœud sera plutôt lente au départ en raison des coûts de conception élevés et des complexités de la première implémentation N3B du nœud, de sorte que la plus grande fonderie du monde ne s’attend pas à ce qu’il soit un contributeur significatif à ses revenus en 2023. Pourtant, le l’entreprise investira des dizaines de milliards de dollars dans l’expansion de sa capacité de fabrication compatible N3, car à terme N3 devrait devenir une famille populaire et durable de nœuds de production pour TSMC.

Rampe lente initialement

“Notre N3 est entré avec succès dans la production en volume à la fin du quatrième trimestre de l’année dernière comme prévu, avec un bon rendement”, a déclaré C. C. Wei, directeur général de TSMC.”Nous nous attendons à une montée en puissance en douceur en 2023, grâce aux applications HPC et aux smartphones. Comme la demande de nos clients en N3 dépasse notre capacité d’approvisionnement, nous prévoyons que le N3 sera pleinement utilisé en 2023.”

Gardant à l’esprit que les dépenses en capital de TSMC en 2021 et 2022 se sont principalement concentrées sur l’expansion de ses capacités de fabrication N5 (classe 5 nm), il est il n’est pas surprenant que la capacité compatible N3 de l’entreprise soit modeste. Pendant ce temps, TSMC ne s’attend pas à ce que N3 représente une part importante de ses revenus avant le troisième trimestre.

En fait, la fonderie n°1 s’attend à ce que les nœuds N3 (qui incluent à la fois le N3 de base et le N3E détendu qui est défini sur entrer dans HVM au second semestre 2023) pour représenter peut-être 4 % à 6 % des revenus de la société en matière de plaquettes en 2023. Et pourtant, cela dépasserait la contribution de N5 au cours de ses deux premiers trimestres de HVM en 2020 (qui était d’environ 3,5 milliards de dollars ).

“Nous prévoyons que [la contribution importante aux revenus de N3] commencera au troisième trimestre 2023 et N3 contribuera pour un pourcentage à un chiffre moyen de nos revenus totaux de plaquettes en 2023″, a déclaré Wei.”Nous prévoyons que les revenus N3 en 2023 seront supérieurs aux revenus N5 au cours de sa première année en 2020.”

De nombreux analystes pensent que la référence N3 (également connue sous le nom de N3B) sera utilisée par Apple exclusivement ou presque exclusivement, qui est le plus gros client de TSMC qui est prêt à adopter des nœuds de pointe avant toutes les autres entreprises, malgré des coûts initiaux élevés. Si cette hypothèse est correcte et qu’Apple est effectivement le principal client à utiliser la ligne de base N3, il convient de noter que TSMC mentionne à la fois le smartphone et le HPC (un terme vague que TSMC utilise pour décrire pratiquement tous les ASIC, CPU, GPU, SoC et FPGA non destinées à l’automobile, aux communications et aux smartphones) en conjonction avec N3 en 2023.

N3E à venir au second semestre

L’une des raisons pour lesquelles de nombreuses entreprises attendent le N3E détendu de TSMC La technologie (qui entre dans HVM dans la seconde moitié de 2023, selon TSMC) est l’amélioration des performances et de la puissance, ainsi qu’une mise à l’échelle logique encore plus agressive. Une autre est que le processus offrira des coûts inférieurs, mais au prix d’un manque de mise à l’échelle de la SRAM par rapport au N5, selon les analystes de China Renaissance.

“Le N3E, avec six couches EUV de moins que le N3 de base, promet une complexité de processus, un coût intrinsèque et un temps de cycle de fabrication plus simples, mais avec un gain de densité moindre”, a écrit Szeho Ng, analyste chez China Renaissance, dans une note aux clients cette semaine.

Ho dit que le N3 original de TSMC comporte jusqu’à 25 couches EUV et peut appliquer plusieurs motifs pour certaines d’entre elles pour une densité supplémentaire. Par contrat, N3E prend en charge jusqu’à 19 couches EUV et n’utilise qu’un EUV à motif unique, ce qui réduit la complexité, mais signifie également une densité plus faible.

“L’intérêt des clients pour le N3E optimisé (après la rampe N3B de base-up, qui est largement limité à Apple) est élevé, englobant les applications à forte intensité de calcul dans HPC (AMD, Intel), mobile (Qualcomm, Mediatek) et ASIC (Broadcom, Marvell) », a écrit Ho.

Il semble que N3E sera en effet le principal cheval de bataille de classe 3 nm de TSMC avant que N3P, N3S et N3X n’arrivent plus tard.

Des dizaines de milliards sur N3

Alors que les nœuds de classe 3nm de TSMC vont rapporter à l’entreprise un peu plus de 4 milliards de dollars en 2023, l’entreprise dépensera des dizaines de milliards de dollars pour étendre sa capacité de fabrication à produire des puces sur divers nœuds N3. Cette année, les dépenses en capital de la société devraient se situer entre 32 et 36 milliards de dollars. 70 % de cette somme sera utilisée pour des technologies de processus avancées (N7 et inférieures), qui incluent une capacité compatible N3 à Taïwan, ainsi que des équipements pour Fab 21 en Arizona (nœuds N4, N5). Pendant ce temps, 20 % seront utilisés pour les fabs produisant des puces sur des technologies spécialisées (ce qui signifie essentiellement une variété de processus de classe 28 nm), et 10 % seront dépensés pour des choses comme l’emballage avancé et la production de masques.

Dépenses à moins de 22 milliards de dollars sur la capacité N3 et N5 indiquent que TSMC est confiant quant à la demande pour ces nœuds. Et il y a une bonne raison à cela: la famille N3 de technologies de processus devrait être la dernière famille de nœuds de production basés sur FinFET de TSMC pour les puces hautes performances complexes. Le processus de fabrication N2 (classe 2 nm) de l’entreprise s’appuiera sur des transistors à effet de champ à grille périphérique (GAAFET) à base de nanofeuilles. En fait, l’analyste Szeho Ng de China Renaissance estime qu’une part importante des CapEx de cette année pour les technologies avancées sera consacrée à la capacité N3, ouvrant la voie au déploiement de N3E, N3P, N3X et N3S. Étant donné que les usines compatibles N3 peuvent également produire des puces sur des processus N5, TSMC pourra utiliser cette capacité là où il y aura également une demande importante de puces basées sur N5.

“TSMC a guidé 2023 CapEx à 32 $-36 milliards (2022 : 36,3 milliards de dollars), avec son expansion concentrée sur N3 dans Fab 18 (Tainan)”, a écrit l’analyste dans une note aux clients.

Étant donné que la technologie de processus N2 de TSMC ne montera en puissance qu’à partir de 2026, N3 sera en effet un nœud durable pour l’entreprise. De plus, comme il s’agira du dernier nœud basé sur FinFET pour les puces avancées, il sera utilisé pendant de nombreuses années car toutes les applications n’auront pas besoin de GAAFET.