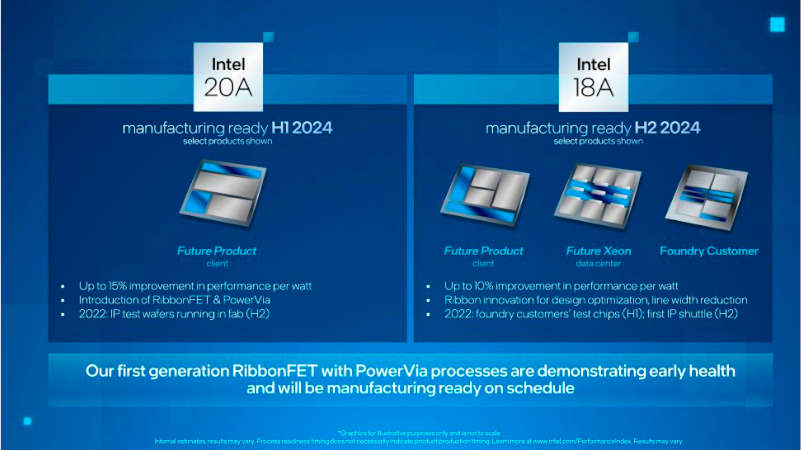

Intel a réalisé des progrès significatifs dans développement des procédés de fabrication Intel 18A (classe 1,8 nm) et Intel 20A (classe 2 nm). Ces processus seront utilisés pour fabriquer des puces pour les produits d’Intel et ses clients de la division Intel Foundry Services (IFS).

Wang Rui, président et président d’Intel Chine, a annoncé que la société avait finalisé le développement de ces processus. Intel a déterminé toutes les spécifications, les matériaux, les exigences et les objectifs de performances pour les deux technologies. Il s’agit d’une étape importante dans le développement de ces processus.

Le processus de fabrication d’Intel 20A utilisera des transistors Gate All Around (GAA) RibbonFET et PowerVia backside power delivery (BPD). Ce processus implique de rétrécir le pas métallique, d’introduire une nouvelle structure de transistor et d’ajouter de la puissance arrière. C’est un défi de taille, mais il permettra à Intel de surpasser ses concurrents TSMC et Samsung Foundry, lui permettant de retrouver son ancienne gloire. Intel prévoit de commencer à utiliser le nœud au premier semestre 2024.

Le processus de fabrication d’Intel 18A affine davantage les technologies RibbonFET et PowerVia de la société pour réduire la taille des transistors. Le développement de ce nœud progresse suffisamment bien pour qu’Intel repousse son introduction de fin 2025 à fin 2024. À l’origine, Intel prévoyait d’utiliser le scanner Twinscan EXE avec une optique à ouverture numérique (NA) de 0,55, High NA d’ASML, pour le nœud 1,8 Angstrom mais a décidé de commencer à utiliser cette technologie tôt, il a donc décidé d’utiliser 0.33NA. La société s’attend à ce que lorsque la technologie de fabrication de classe 1,8 nm entrera en HVM (High Volume Manufacturing) au second semestre 2024, elle deviendra le nœud le plus avancé du secteur.