Letzte Woche veröffentlichte TSMC seine Ergebnisberichte für das vierte Quartal und das Gesamtjahr 2022 für das Unternehmen. Neben der Bestätigung, dass TSMC ein sehr arbeitsreiches, sehr profitables Jahr für die weltweit führende Chipfabrik abschloss – mit einem Nettogewinn von fast 34 Milliarden US-Dollar für das Jahr – hat uns der Jahresabschlussbericht des Unternehmens auch ein neues Update gegeben den Stand der verschiedenen Fab-Projekte von TSMC.

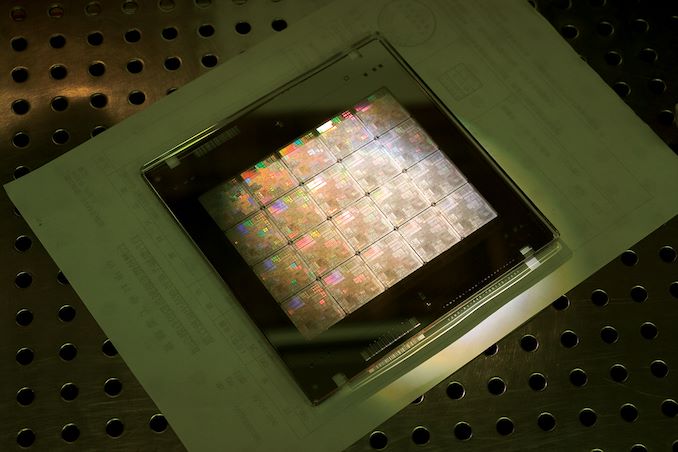

Die große Neuigkeit von TSMC für Q4’22 ist, dass TSMC mit der Massenfertigung von Chips auf seiner N3-Fertigungstechnologie (3-nm-Klasse) begonnen hat. Die Rampe dieses Knotens wird aufgrund der hohen Designkosten und der Komplexität der ersten N3B-Implementierung des Knotens zunächst eher langsam sein, sodass die weltweit größte Foundry nicht erwartet, dass sie 2023 einen wesentlichen Beitrag zu ihren Einnahmen leisten wird Das Unternehmen wird zig Milliarden Dollar in die Erweiterung seiner N3-fähigen Produktionskapazität investieren, da erwartet wird, dass N3 schließlich zu einer beliebten, langlebigen Familie von Produktionsknoten für TSMC wird.

Zunächst langsamer Anstieg

“Unser N3 ist wie geplant Ende des vierten Quartals letzten Jahres erfolgreich in die Volumenproduktion eingetreten, mit guter Ausbeute”, sagte C. C. Wei, Chief Executive von TSMC.”Wir erwarten einen reibungslosen Anstieg im Jahr 2023, der sowohl von HPC-als auch von Smartphone-Anwendungen angetrieben wird. Da die Nachfrage unserer Kunden nach N3 unsere Lieferfähigkeit übersteigt, erwarten wir, dass N3 im Jahr 2023 voll ausgelastet sein wird.”

Wenn man bedenkt, dass sich die Investitionen von TSMC in den Jahren 2021 und 2022 hauptsächlich auf die Erweiterung seiner N5-Fertigungskapazitäten (5-nm-Klasse) konzentrierten, ist dies der Fall nicht überraschend, dass die N3-fähige Kapazität des Unternehmens bescheiden ist. In der Zwischenzeit erwartet TSMC nicht, dass N3 vor dem dritten Quartal einen nennenswerten Anteil an seinen Einnahmen ausmachen wird.

Tatsächlich erwartet die Gießerei Nr. 1 N3-Knoten (die sowohl N3 als Basislinie als auch entspanntes N3E umfassen, das darauf eingestellt ist Eintritt in HVM in der zweiten Hälfte des Jahres 2023) auf vielleicht 4 % bis 6 % des Waferumsatzes des Unternehmens im Jahr 2023. Und doch würde dies den Beitrag von N5 in den ersten beiden Quartalen von HVM im Jahr 2020 (der etwa 3,5 Milliarden US-Dollar betrug) übersteigen ).

“Wir gehen davon aus, dass [ein beträchtlicher N3-Umsatzbeitrag] im dritten Quartal 2023 beginnen wird und N3 im Jahr 2023 einen mittleren einstelligen Prozentsatz unseres gesamten Waferumsatzes beitragen wird”, sagte Wei.”Wir erwarten, dass die N3-Einnahmen im Jahr 2023 höher sein werden als die N5-Einnahmen in seinem ersten Jahr im Jahr 2020.”

Viele Analysten glauben, dass die Baseline N3 (auch bekannt als N3B) entweder ausschließlich oder ausschließlich von Apple verwendet wird fast ausschließlich, das ist der größte Kunde von TSMC, der trotz hoher Anfangskosten bereit ist, Spitzenknoten vor allen anderen Unternehmen einzuführen. Wenn diese Annahme richtig ist und Apple tatsächlich der Hauptkunde ist, der Baseline N3 verwendet, dann ist es bemerkenswert, dass TSMC sowohl Smartphone als auch HPC erwähnt (ein vager Begriff, den TSMC verwendet, um praktisch alle ASICs, CPUs, GPUs, SoCs und FPGAs nicht zu beschreiben ausgerichtet auf Automobil-, Kommunikations-und Smartphone-Anwendungen) in Verbindung mit N3 im Jahr 2023.

N3E kommt in der zweiten Hälfte

Einer der Gründe, warum viele Unternehmen auf die entspannte N3E von TSMC warten Technologie (die laut TSMC in der zweiten Hälfte des Jahres 2023 in HVM eingeführt wird) sind die höheren Leistungs-und Leistungsverbesserungen sowie eine noch aggressivere Logikskalierung. Ein weiterer Grund ist, dass der Prozess niedrigere Kosten bietet, wenn auch auf Kosten eines fehlende SRAM-Skalierung im Vergleich zu N5, laut Analysten von China Renaissance.

„N3E verspricht mit sechs EUV-Schichten weniger als das Basismodell N3 eine einfachere Prozesskomplexität, intrinsische Kosten und Fertigungszykluszeit, wenn auch mit weniger Dichtegewinn“, schrieb Szeho Ng, Analyst bei China Renaissance, diese Woche in einer Mitteilung an Kunden.

Ho sagt, dass der ursprüngliche N3 von TSMC bis zu 25 EUV-Schichten aufweist und für einige von ihnen mehrere Muster für zusätzliche Dichte anwenden kann. Vertraglich unterstützt N3E bis zu 19 EUV-Layer und verwendet nur Single-Patterning-EUV, was die Komplexität reduziert, aber auch eine geringere Dichte bedeutet. up, das weitgehend auf Apple beschränkt ist) ist hoch und umfasst rechenintensive Anwendungen in HPC (AMD, Intel), Mobilgeräten (Qualcomm, Mediatek) und ASICs (Broadcom, Marvell)”, schrieb Ho.

Es sieht so aus, als ob N3E tatsächlich das Hauptarbeitspferd der 3-nm-Klasse von TSMC sein wird, bevor später N3P, N3S und N3X eintreffen.

Dutzende Milliarden auf N3

Während die 3-nm-Klasse-Knoten von TSMC dem Unternehmen im Jahr 2023 etwas mehr als 4 Milliarden US-Dollar einbringen werden, wird das Unternehmen zig Milliarden US-Dollar ausgeben, um seine Fab-Kapazität zu erweitern, um Chips auf verschiedenen N3-Knoten zu produzieren. In diesem Jahr werden die Investitionsausgaben des Unternehmens auf 32 bis 36 Milliarden US-Dollar geschätzt. 70 % dieser Summe werden für fortschrittliche Prozesstechnologien (N7 und darunter) verwendet, darunter N3-fähige Kapazitäten in Taiwan sowie Ausrüstung für Fab 21 in Arizona (N4-, N5-Knoten). In der Zwischenzeit werden 20 % für Fabriken verwendet, die Chips mit Spezialtechnologien herstellen (was im Wesentlichen eine Vielzahl von Prozessen der 28-nm-Klasse bedeutet), und 10 % werden für Dinge wie fortschrittliche Verpackung und Maskenproduktion ausgegeben.

Ausgaben bei Mindestens 22 Milliarden US-Dollar an N3-und N5-Kapazität zeigen, dass TSMC von der Nachfrage nach diesen Knoten überzeugt ist. Und das aus gutem Grund: Die N3-Familie von Prozesstechnologien wird TSMCs letzte FinFET-basierte Familie von Produktionsknoten für komplexe Hochleistungschips sein. Der N2-Herstellungsprozess (2-nm-Klasse) des Unternehmens wird auf Nanoblatt-basierten Allround-Feldeffekttransistoren (GAAFETs) basieren. Tatsächlich glaubt Analyst Szeho Ng von China Renaissance, dass ein erheblicher Teil der diesjährigen Investitionsausgaben für fortschrittliche Technologien für N3-Kapazität ausgegeben wird, was den Grundstein für die Einführung von N3E, N3P, N3X und N3S legt. Da N3-fähige Fabriken auch Chips mit N5-Prozessen produzieren können, wird TSMC diese Kapazität dort nutzen können, wo es auch eine erhebliche Nachfrage nach N5-basierten Chips geben wird.

“TSMC prognostizierte die CapEx für 2023 mit 32 $ 36 Milliarden (2022: 36,3 Milliarden US-Dollar), wobei sich die Expansion auf N3 in Fab 18 (Tainan) konzentriert“, schrieb der Analyst in einer Mitteilung an Kunden.

Da die N2-Prozesstechnologie von TSMC erst ab 2026 hochgefahren wird, wird N3 in der Tat ein langlebiger Knotenpunkt für das Unternehmen sein. Da es außerdem der letzte FinFET-basierte Knoten für fortschrittliche Chips sein wird, wird es noch viele Jahre verwendet werden, da nicht alle Anwendungen GAAFETs benötigen werden.